- 4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE FULL

- 4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE CODE

A continuous assignment statement assigns values to the wire datatype and makes a connection to an actual wire in the circuit. Here we declare the data types of the arguments used in the instantiation of the demultiplexer design.

But we do not specify any ports in this module as there will be ports inside the testbench and not outside. The next line declares the name of the module for testbench according to the syntax as mentioned above. It is followed by the file name in inverted commas. We start by writing 'include which is a keyword to include a file. The following line includes the pre-written file Demultiplexer_1_to_4_case.v into the testbench. The test bench is the file through which we give inputs and observe the outputs.

4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE FULL

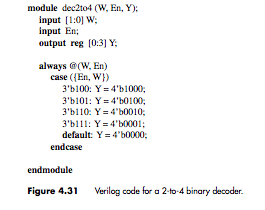

Here is the full code: module Demultiplexer_1_to_4_case (output reg Y, input A, input din) Ģ'b00 : begin Y = din Y = 0 endĢ'b10 : begin Y = din Y = 0 endĢ'b11 : begin Y = din Y = 0 endĮndmodule Test bench for the demultiplexer Observe that we are not specifying the structure of the circuit, we are only creating the logic of the circuit which can implement that hardware. This modeling is based on the behavior of the circuit hence it is called behavioral modeling. After this, those statements are mentioned, such as the output port Y should be attached to the din, Y to 0, and so on, according to the truth table. The terms begin and end are part of the Verilog syntax if you are writing more than one statement in that block. The colon then marks the end of a case item and starts the action that must happen in that particular case. These cases indicate that, according to the value of A, one of the four statements is selected. So, now we can write case (A)Īs we see here in the first case, 2'b00 represents the case when the input A is 2'b00. If the expression corresponds to any of the case_item, then those design statements are executed. First, let us see the general format to write a case statement in Verilog. The case statement in Verilog is analogous to switch-case in C language. Then inside always block we write, case (A)

4 TO 16 DECODER USING 2 TO 4 DECODER VERILOG CODE CODE

* would mean that the code itself has to decide on the input signals of the sensitivity list. Note that the always statement always A) could be written as always *. In Verilog, begin embarks and end concludes any block which contains more than one statement in it. is a part of the syntax, used before the sensitivity list. It controls when the statements in the always block are to be evaluated. The sensitivity list includes all input signals used by the always block. (Y, A) is known as the sensitivity list or the trigger list. Using the always statement, a procedural statement in Verilog, we will run the program sequentially.

Next up, since its behavioral modeling style, here comes the always statement. here signifies that the output is of 4 bits. module Demultiplexer_1_to_4_case (Y, A, din) The reg data object holds its value from one procedural assignment statement to the next and means it holds its value over simulation data cycles.Īnother style of declaration in the port list is to declare the port size and port direction after the module declaration. Hence, states that the port named as A is a vector with MSB = 1 and LSB = 0. If a port has multiple bits, then it is known as a vector. Taking into consideration the first line of the code, Demultiplexer_1_to_4_case is the identifier, the input is called port direction.

0 kommentar(er)

0 kommentar(er)